INTEL SDM Vol.3 (System Programming) - SYSTEM ARCHITECTURE OVERVIEW 번역 및 정리

- -

하드웨어 및 커널 공부를 위해(사실 하이퍼바이저 공부를 위해) 선행되어야만 하는 지식들(용어만 알고 있거나, 잘 모르는 것들)이 INTEL SDM에 정말 자세하게 나와있는데, 전부 영어여서 Notion + AI, 후처리를 통해서 번역 및 요약해봤습니다.

Chapter 별로 하나씩 번역해볼 예정입니다. (약 700장정도의 분량)

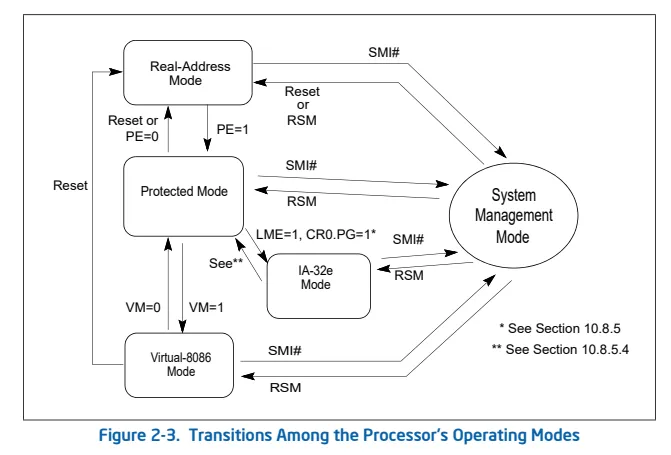

IA-32 아키텍처의 운영 모드:

- Protected Mode (보호 모드)

- 프로세서의 기본 운영 모드.

- 고성능과 유연성 제공.

- 과거 소프트웨어와의 호환성 유지.

- 메모리 보호, 멀티태스킹 같은 고급 기능 사용 가능.

- Real-Address Mode (실제 주소 모드)

- Intel 8086 프로세서와 유사한 환경 제공.

- 간단한 프로그래밍 모델.

- Protected Mode 또는 System Management Mode(SMM)로 전환 가능.

- System Management Mode (SMM)

- 전원 관리와 OEM 차별화 기능 지원.

- SMI# 핀 신호를 통해 진입.

- SMM으로 전환 시:

- 현재 실행 중인 프로그램의 상태(컨텍스트) 저장.

- 독립된 별도 주소 공간에서 SMM 전용 코드 실행.

- SMM 종료 후 이전 상태로 복귀.

- Virtual-8086 Mode (가상 8086 모드)

- Protected Mode에서 지원하는 유사 운영 모드.

- 8086 소프트웨어를 멀티태스킹 환경에서 실행 가능.

- 주로 과거 소프트웨어와의 호환성 유지에 사용.

Intel 64 아키텍처의 추가 모드:

- IA-32e Mode

- 두 가지 하위 모드 지원:

- Compatibility Mode (호환 모드):

- 대부분의 과거 Protected Mode 애플리케이션이 변경 없이 실행 가능.

- 64-Bit Mode (64비트 모드):

- 64비트 선형 주소 지원.

- 64GB 이상의 물리적 메모리 접근 가능.

- Compatibility Mode (호환 모드):

- 두 가지 하위 모드 지원:

모드 간 전환:

- 모드 전환은 소프트웨어 또는 하드웨어 이벤트에 따라 발생.

- SMM처럼 외부 인터럽트에 의해 진입하거나, Protected Mode에서 Virtual-8086 Mode로 진입 등 다양한 전환 경로가 있음.

- 아키텍처가 각 모드 간 전환을 투명하게 지원.

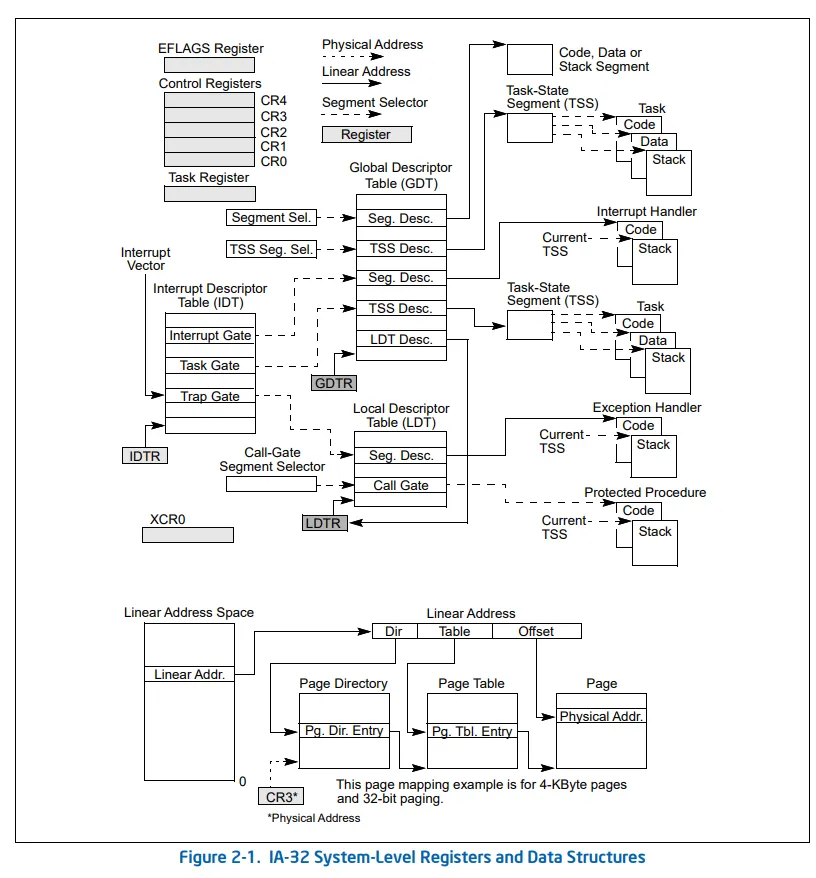

Protected Mode 에서의 메모리 접근

1. 메모리 접근의 기본 메커니즘

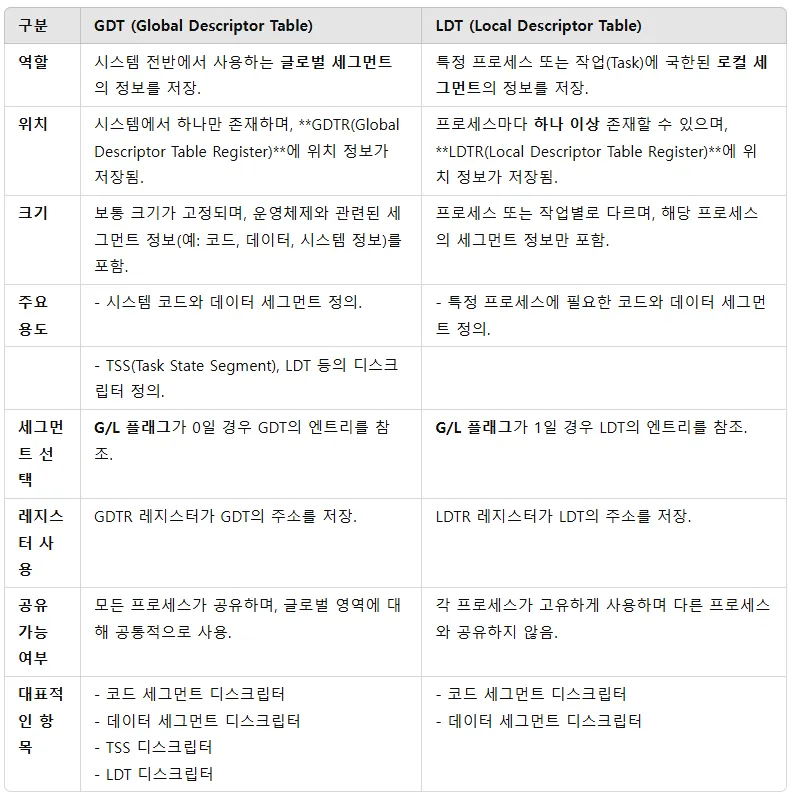

- Global Descriptor Table (GDT) 또는 Local Descriptor Table (LDT)를 통해 메모리 접근이 이루어짐.

- GDT와 LDT는 세그먼트 디스크립터(segment descriptor)라는 항목을 포함하고 있음.

- 세그먼트 디스크립터에는 다음 정보가 포함됨:

- 세그먼트의 시작 주소(base address)

- 접근 권한(access rights)

- 세그먼트의 유형(type)

- 사용 상태(usage information)

- 세그먼트 디스크립터에는 다음 정보가 포함됨:

2. 세그먼트 셀렉터(segment selector)

- 세그먼트 디스크립터에 접근하기 위해 사용하는 인덱스.

- GDT 또는 LDT의 특정 위치(offset)를 가리킴.

- 구성 요소:

- 인덱스(Index): GDT 또는 LDT 내 디스크립터의 위치.

- G/L 플래그(Global/Local Flag): GDT인지 LDT인지 구분.

- 접근 권한 정보(Access Rights): 현재 실행 중인 코드의 권한과 비교하여 접근 가능 여부 결정.

3. 메모리 접근 절차

- 세그먼트 셀렉터(segment selector)와 오프셋(offset)을 통해 접근.

- 세그먼트 셀렉터는 GDT 또는 LDT의 세그먼트 디스크립터로 접근.

- 세그먼트 디스크립터에서 해당 세그먼트의 시작 주소(base address)를 가져옴.

- 오프셋을 더해 최종적으로 선형 주소(linear address) 계산.

- 이후 페이징 메커니즘을 통해 물리 주소(physical address)로 변환.

4. 특별한 레지스터

- GDTR (Global Descriptor Table Register):

- GDT의 선형 주소(linear address) 저장.

- LDTR (Local Descriptor Table Register):

- LDT의 선형 주소(linear address) 저장.

- TR (Task Register):

- 현재 작업(task) 상태를 나타내는 TSS(Task-State Segment)를 가리킴.

5. Current Privilege Level (CPL)

- 현재 실행 중인 코드의 보호 수준(Privilege Level).

- 접근하려는 세그먼트의 접근 권한과 CPL을 비교하여 접근 가능 여부 결정.

6. 페이징과 연계

- Protected Mode에서는 선형 주소가 페이징 메커니즘에 의해 물리 주소로 변환됨.

- 페이징 단계:

- PML4 -> Page Directory -> Page Table 순서로 주소 변환.

- 4KB 페이지와 4단계 페이징 구조를 통해 큰 메모리 공간 지원.

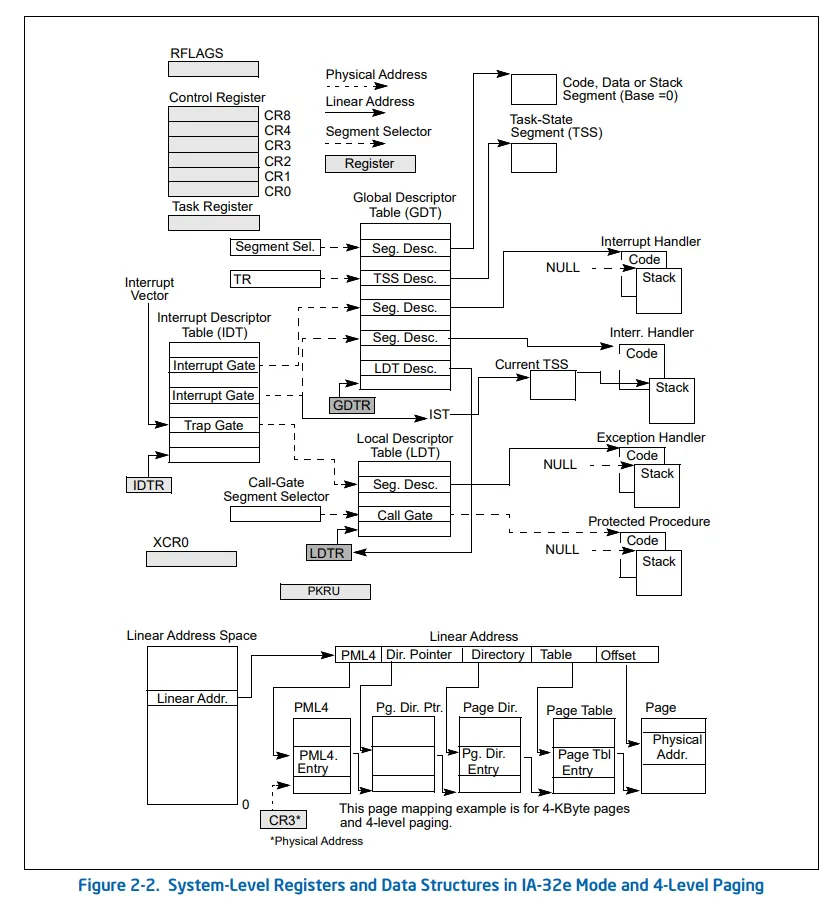

IA-32e 모드에서의 글로벌 및 로컬 디스크립터 테이블 (GDT, LDT)

- GDTR 및 LDTR 레지스터:

- IA-32e 모드(64비트 모드와 호환 모드)에서 64비트로 확장됨.

- 세부 내용은 섹션 3.5.2 "IA-32e 모드의 세그먼트 디스크립터 테이블"을 다룰 때 포스팅 예정

- 64비트 모드:

- GDT와 LDT는 64비트 베이스 주소를 지원하도록 확장됨.

- LDT 디스크립터는 16바이트로 구성되며, 64비트 베이스 주소와 다양한 속성을 포함.

- 호환 모드에서는 디스크립터가 확장되지 않음.

시스템 세그먼트, 세그먼트 디스크립터 및 게이트

- 시스템 세그먼트:

- TSS(Task-State Segment)와 LDT(Local Descriptor Table) 정의.

- GDT는 세그먼트로 간주되지 않음(세그먼트 선택자와 디스크립터를 통해 접근하지 않음).

- 왜?

- GDT는 GDTR(Global Descriptor Table Register)로 직접 참조되며, 세그먼트 선택자를 통해 간접적으로 접근되지 않기 때문

- GDT는 세그먼트처럼 실행되거나 접근되지 않음 (한 마디로 그냥 세그먼트를 모아둔 것에 불과하다는 뜻)

- 왜?

- 게이트(Gates):

- 유형: 호출 게이트(Call Gate), 인터럽트 게이트(Interrupt Gate), 트랩 게이트(Trap Gate), 태스크 게이트(Task Gate).

- 역할: 다른 권한 수준에서 실행되는 시스템 절차 및 핸들러로의 보호된 접근 제공.

- 예: 호출 게이트를 통해 낮은 권한 수준(더 높은 권한)의 코드 세그먼트로 접근 가능.

- 게이트 동작:

- 호출 프로시저는 게이트를 가리키는 세그먼트 선택자를 제공.

- 프로세서는 현재 권한 수준(CPL)과 게이트 및 대상 코드 세그먼트의 권한 수준을 비교하여 접근 권한 확인.

- 접근 허용 시:

- 대상 코드 세그먼트의 세그먼트 선택자와 오프셋을 가져옴.

- 권한 수준 변경 시, 대상 권한 수준의 스택으로 전환:

- TSS에서 새로운 스택의 세그먼트 선택자를 가져옴.

- 16비트와 32비트 코드 세그먼트 간의 전환도 지원.

2.1.3 Task-State 세그먼트 및 Task 게이트

TSS(Task-State Segment)의 역할

- TSS란?: 태스크의 실행 환경 상태를 정의하는 데이터 구조.

- 포함하는 내용:

- 범용 레지스터 상태.

- 세그먼트 레지스터 상태.

- EFLAGS, EIP(Instruction Pointer) 레지스터.

- 3개의 스택 세그먼트의 세그먼트 선택자와 스택 포인터(각 권한 수준에 하나씩).

- 현재 태스크와 관련된 LDT의 세그먼트 선택자.

- 페이징 구조 계층의 베이스 주소(CR3).

Protected Mode에서 태스크 전환

- 모든 프로그램 실행은 현재 태스크(Current Task) 컨텍스트에서 이루어짐.

- *Task Register(TR)**에 현재 태스크의 TSS 세그먼트 선택자가 저장됨.

- 태스크 전환 방법:

- CALL 또는 JMP 명령어를 사용하여 새로운 태스크로 전환 가능.

- 명령어에 새로운 태스크의 TSS 세그먼트 선택자가 포함됨.

태스크 전환 시 프로세서 동작

- 현재 태스크 상태 저장:

- 현재 태스크의 상태를 TSS에 저장.

- Task Register(TR) 업데이트:

- 새로운 태스크의 TSS 세그먼트 선택자로 갱신.

- GDT에서 새로운 TSS 접근:

- 새로운 TSS의 세그먼트 디스크립터를 GDT에서 가져옴.

- 새로운 태스크 상태 로드:

- 새 TSS에 저장된 정보를 다음 레지스터와 데이터 구조로 로드:

- 범용 레지스터, 세그먼트 레지스터, LDTR.

- CR3(페이징 구조 계층의 베이스 주소).

- EFLAGS, EIP.

- 새 TSS에 저장된 정보를 다음 레지스터와 데이터 구조로 로드:

- 새 태스크 실행:

- 새 태스크의 실행 시작.

Task Gate

- 기능: 태스크 접근을 위한 게이트.

- 차이점:

- Call Gate는 코드 세그먼트에 접근하지만, Task Gate는 TSS에 접근.

- Task Gate는 세그먼트 선택자를 통해 TSS를 참조.

- 사용 목적:

- 태스크 간의 안전한 전환 제공.

1. IA-32e 모드에서 하드웨어 작업 전환이 지원되지 않음

- 64비트 모드에서는 하드웨어 기반 작업 전환 기능이 제거되었습니다.

- CPU가 TSS를 이용해 자동으로 작업 전환을 수행하지 않습니다.

- 대신 TSS는 특정한 시스템 정보를 저장하는 데 사용됩니다.

2. 64비트 TSS에 포함된 주요 정보

- 권한 수준별 스택 포인터 주소

- 각 권한 레벨(Privilege Level, Ring 0~3)에 대한 스택 포인터 정보를 저장합니다.

- 권한 레벨 변경(예: 사용자 모드에서 커널 모드로 전환) 시 올바른 스택을 사용할 수 있도록 합니다.

- 인터럽트 스택 테이블(IST) 포인터 주소

- 인터럽트 처리 시 사용할 독립적인 스택 주소를 포함합니다.

- 특정 예외(Double Fault 등)나 치명적 상황에서 기존 스택 대신 안정적인 스택을 제공하기 위해 사용됩니다.

- IO-권한 비트맵(IO-Permission Bitmap) 오프셋 주소

- TSS 기본 주소(base)로부터 오프셋을 계산하여 IO 권한 비트맵의 위치를 지정합니다.

- IO 비트맵은 각 프로세스가 특정 입출력 포트에 접근할 수 있는 권한을 제어합니다.

IO 비트맵(IO-Permission Bitmap)

IO 비트맵은 IA-32 및 IA-32e 아키텍처에서 프로세스의 입출력 포트(IO Port) 접근을 제어하기 위한 데이터 구조입니다. Task-State Segment(TSS)의 일부로 포함되며, 특정 프로세스가 어떤 IO 포트에 접근할 수 있는지 결정합니다.

IO 비트맵의 주요 특징

- 위치

- TSS(Task-State Segment) 내부에 포함됩니다.

- TSS의 기본 주소(base address)로부터 오프셋(offset) 값을 사용하여 IO 비트맵의 위치를 지정합니다.

- 구조

- IO 비트맵은 1비트 당 하나의 IO 포트를 나타냄.

- 1이면 해당 포트에 접근이 허용되지 않음.

- 0이면 접근이 허용됨.

- IO 비트맵의 길이는 최대 64KB로, 0번부터 65535번까지의 IO 포트를 제어할 수 있습니다.

- IO 비트맵은 1비트 당 하나의 IO 포트를 나타냄.

- 활용

- 각 비트는 특정 IO 포트를 나타내며, 프로세스마다 다른 IO 비트맵을 설정하여 세분화된 IO 접근 제어가 가능합니다.

- 커널 또는 하드웨어가 IO 비트맵을 읽어, 해당 포트에 대한 접근을 허용하거나 차단합니다.

3. Task Register(TR)의 확장

- 64비트 모드에서는 Task Register가 64비트 주소를 저장하도록 확장되었습니다.

- TR은 활성화된 TSS의 기본 주소를 가리키며, CPU가 필요한 정보를 TSS에서 가져올 수 있도록 합니다.

4. TSS의 현대적 사용

- 하드웨어 작업 전환이 제거되었지만, TSS는 다음과 같은 목적으로 여전히 사용됩니다:

- 스택 관리

- 권한 수준 전환 및 인터럽트 처리 시 안정적인 스택 전환을 지원.

- IO 접근 제어

- 특정 프로세스가 IO 포트에 접근할 수 있는지 제어.

- 시스템 안정성 향상

- 인터럽트 스택 테이블을 통해 치명적 예외 상황에서의 시스템 안정성을 확보.

- 스택 관리

2.1.4 인터럽트 및 예외 Handling

1. 개요

- 인터럽트와 예외 처리는 Interrupt Descriptor Table(IDT)를 통해 이루어짐.

- IDT는 게이트 디스크립터(gate descriptor)의 집합으로, 각각의 디스크립터는 특정 인터럽트 또는 예외 핸들러에 대한 정보를 포함.

- IDT는 세그먼트가 아니며, IDT의 시작 주소(선형 주소)는 IDT 레지스터(IDTR에 저장됨.

2. IDT의 동작

- 인터럽트 벡터 수신:

- 내부 하드웨어, 외부 인터럽트 컨트롤러, 또는 소프트웨어 명령어(INT n, INTO, INT3 등)에 의해 발생.

- 이 벡터는 IDT의 인덱스로 사용됨.

- 게이트 디스크립터 접근:

- 인터럽트 게이트, 트랩 게이트, 또는 태스크 게이트일 수 있음.

- 핸들러 호출:

- 인터럽트 게이트 또는 트랩 게이트: 핸들러를 호출하는 방식이 Call Gate와 유사.

- 태스크 게이트: 태스크 전환(task switch)을 통해 핸들러에 접근.

2.1.4.1 Interrupt and Exception Handling in IA-32e Mode

1. IA-32e 모드의 특징

- IDT의 게이트 디스크립터가 16바이트로 확장됨:

- 64비트 기반 주소를 지원하기 위해.

- 64비트 모드와 호환 모드 모두 동일하게 적용.

- IDTR:

- IDT의 시작 주소를 저장하는 IDTR도 64비트 주소를 지원하도록 확장됨.

- 태스크 게이트 지원 중단:

- IA-32e 모드에서는 태스크 게이트를 사용할 수 없음.

2.1.5 Memory Management

1. 개요

- 시스템 아키텍처는 두 가지 메모리 관리 방식을 지원:

- 직접 물리 주소 지정:

- 선형 주소를 물리 주소로 그대로 사용.

- 가상 메모리 (페이징 사용):

- 선형 주소를 여러 단계의 페이징 구조를 통해 물리 주소로 변환.

- 직접 물리 주소 지정:

2. 페이징 메커니즘

- 페이징 구조:

- 페이지 프레임(page frame)의 물리적 위치는 페이징 구조에 저장.

- 페이징 구조는 물리 메모리에 존재하며, 가장 최근에 접근된 페이지만 물리 메모리에 유지 가능.

- CR3 레지스터:

- 페이징 구조 계층의 기본 물리 주소를 저장.

- 각 테이블 엔트리는 페이지 프레임의 시작 주소, 접근 권한, 메모리 관리 정보를 포함.

- 선형 주소 변환 과정:

- 선형 주소를 여러 부분으로 나누어 각 부분이 페이징 구조 계층의 오프셋 역할을 함.

- 페이징 구조를 따라 최종 물리 주소를 계산.

- 계층적 구조:

- 시스템은 단일 계층 또는 여러 계층의 페이징 구조를 가질 수 있음.

- 예를 들어, 태스크마다 독립적인 페이징 구조를 사용할 수 있음.

요약

- Interrupt and Exception Handling:

- IDT를 통해 인터럽트와 예외 처리.

- IA-32e 모드에서는 64비트 주소 지원을 위해 IDT 디스크립터와 IDTR이 확장되었으며, 태스크 게이트는 지원하지 않음.

- Memory Management:

- 물리 주소 지정 또는 가상 메모리(페이징) 방식 지원.

- 페이징 구조는 CR3 레지스터를 통해 관리되며, 선형 주소는 페이징 계층을 따라 물리 주소로 변환.

- 가상 메모리는 효율적인 메모리 사용과 프로세스 격리를 가능하게 함.

2.1.5 IA-32e 모드에서의 메모리 관리 (2.1.5.1 Memory Management in IA-32e Mode)

1. IA-32e 모드의 페이징 구조

IA-32e 모드에서는 4단계 또는 5단계 페이징 구조를 사용합니다.

페이징 구조는 선형 주소(linear address)를 물리 주소(physical address)로 변환하는 데 필요한 정보를 계층적으로 저장합니다.

1.1. 계층 구조

- 5단계 페이징 활성화 시: PML5 → PML4 → Page Directory Pointer → Page Directory → Page Table

- 4단계 페이징 활성화 시: PML4 → Page Directory Pointer → Page Directory → Page Table

2. 각 단계의 역할과 데이터 구조

2.1. PML5 (Page Map Level 5)

- 5단계 페이징에서 추가되는 최상위 계층입니다.

- PML5 테이블의 각 엔트리에는 다음 정보가 저장됩니다:

- PML4 테이블의 물리적 주소.

- 접근 권한 및 메모리 관리 정보.

- PML5 테이블의 기본 물리 주소는 CR3 레지스터에 저장됩니다.

- 4단계 페이징에서는 PML4 테이블의 주소가 CR3에 저장됩니다.

2.2. PML4 (Page Map Level 4)

- 5단계 페이징에서는 PML5 아래에 위치하며, 4단계 페이징에서는 최상위 계층.

- PML4 테이블의 각 엔트리에는 다음 정보가 포함됩니다:

- Page Directory Pointer Table의 물리적 주소.

- 접근 권한 및 메모리 관리 정보.

2.3. Page Directory Pointer Table

- PML4 테이블 아래 계층.

- 각 엔트리는 Page Directory Table의 물리적 주소, 접근 권한, 메모리 관리 정보를 포함합니다.

2.4. Page Directory

- Page Directory Pointer Table 아래 계층.

- 각 엔트리는 Page Table의 물리적 주소, 접근 권한, 메모리 관리 정보를 포함합니다.

2.5. Page Table

- Page Directory 아래 계층으로, 실제 **페이지 프레임(page frame)**에 대한 정보를 포함합니다.

- 각 엔트리에는:

- 물리 메모리 페이지의 시작 주소.

- 페이지 접근 권한 및 메모리 관리 정보.

3. 동작 과정

- CPU가 선형 주소(linear address)를 참조합니다.

- 선형 주소는 페이징 구조의 여러 계층을 거쳐 최종적으로 물리 주소(physical address)로 변환됩니다.

- 각 계층의 엔트리를 참조하여 다음 계층의 주소를 결정.

- 최종적으로 Page Table에서 물리 메모리 페이지의 주소를 얻습니다.

4. 5단계 페이징의 필요성

- 5단계 페이징은 물리 메모리와 선형 주소 공간이 증가하면서 추가된 구조입니다.

- 4단계 페이징은 최대 48비트의 선형 주소(256TB)를 지원하지만, 5단계 페이징은 최대 57비트의 선형 주소(128PB)를 지원합니다.

2.1.6 시스템 레지스터(System Registers)

이 내용은 IA-32와 Intel 64 아키텍처에서 시스템 초기화 및 제어를 위한 주요 시스템 레지스터와 관련된 정보를 설명하고 있습니다. 주요 레지스터와 역할을 정리하면 다음과 같습니다.

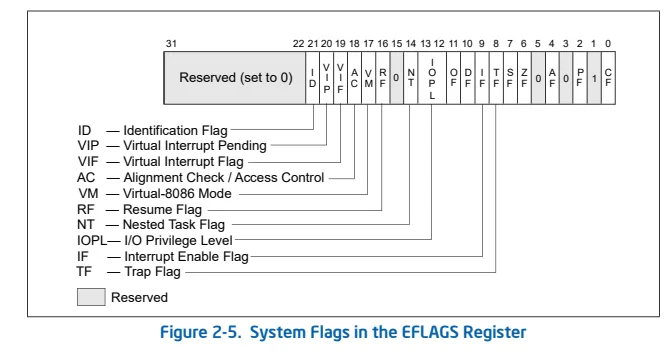

1. EFLAGS 레지스터

- EFLAGS 레지스터는 시스템 플래그와 IOPL 필드를 포함하여 프로세서의 동작을 제어.

- 주요 기능:

- 작업(task) 전환.

- 운영 모드 변경.

- 인터럽트 처리.

- 명령어 추적.

- 접근 권한 제어.

- 자세한 정보는 섹션 2.3에서 설명 예정.

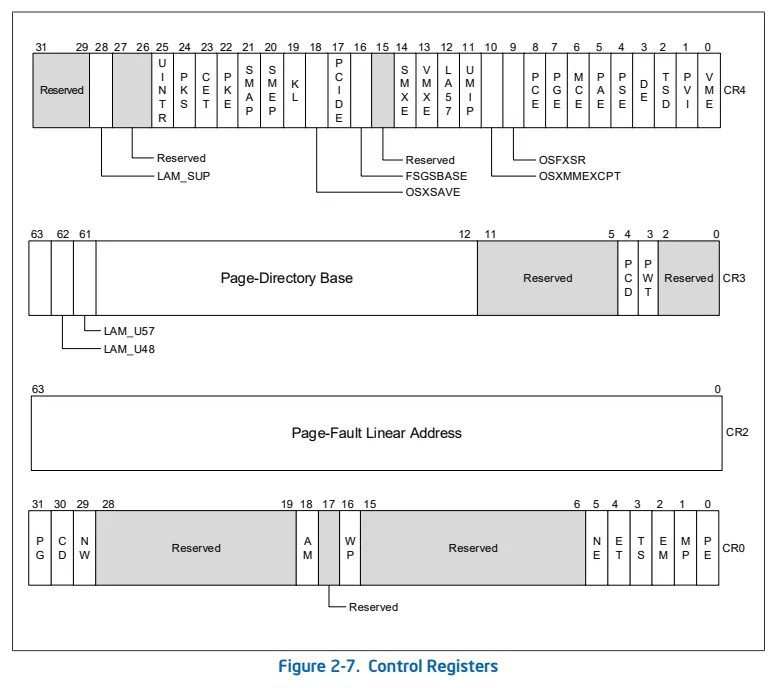

2. 제어 레지스터(Control Registers)

- CR0, CR2, CR3, CR4와 같은 제어 레지스터는 시스템의 주요 동작을 제어하기 위한 플래그와 데이터를 포함.

- 각 레지스터의 역할:

- CR0: 보호 모드 활성화, 페이징 활성화 등 기본 시스템 동작 제어.

- CR2: 페이지 폴트가 발생한 주소 저장.

- CR3: 페이징 구조의 PML4 테이블 또는 디렉터리의 물리 주소 저장.

- CR4: 추가 기능(예: PAE, SMAP 등) 활성화.

- 확장된 제어 레지스터 XCR0에 대한 자세한 정보는 섹션 2.6에서 설명 예정.

3. 디버그 레지스터(Debug Registers)

- 디버깅 목적으로 중단점(breakpoints)을 설정할 수 있는 레지스터.

- 프로그램 및 시스템 소프트웨어 디버깅에 사용.

- 자세한 정보는 19장에서 확인 가능.

4. 메모리 관리 레지스터

- GDTR, LDTR, IDTR:

- 각각 GDT, LDT, IDT 테이블의 **선형 주소와 크기(한계값)**를 저장.

- Task Register (TR):

- 현재 작업에 대한 TSS의 선형 주소와 크기 저장.

- 자세한 정보는 섹션 2.4에서 제공.

5. 모델 특화 레지스터(Model-Specific Registers, MSRs)

- 특정 프로세서 기능을 제어하거나 설정하기 위한 레지스터.

- 주요 기능:

- 디버그 확장.

- 성능 모니터링 카운터.

- 메모리 타입 범위 레지스터(MTRR).

- 머신 체크 아키텍처(MCA).

- MSR의 수와 기능은 프로세서 모델에 따라 다름.

- 자세한 정보는 11.4 섹션 및 4권의 MSR 관련 장에서 제공.

6. 접근 권한

- 대부분의 시스템 레지스터는 특권 레벨 0에서만 접근 가능.

- EFLAGS 레지스터는 애플리케이션 프로그램에서도 제한적으로 접근 가능.

- 예외적으로, 모든 프로그램이 특권 레벨 0에서 실행되도록 설계된 시스템에서는 애플리케이션이 시스템 레지스터를 수정할 수 있음.

정리

- EFLAGS 레지스터: 작업 전환, 인터럽트 처리, 접근 권한 제어 등.

- 제어 레지스터 (CR0~CR4, XCR0): 시스템 동작 제어와 메모리 관리.

- 디버그 레지스터: 디버깅 도구로 사용.

- 메모리 관리 레지스터: GDT, IDT, TSS 등 테이블의 주소와 크기 관리.

- 모델 특화 레지스터(MSR): 프로세서별 고유 기능 제어.

시스템 플래그와 IOPL 필드

1. 시스템 플래그(System Flags)

시스템 플래그는 EFLAGS 레지스터(또는 RFLAGS 레지스터)에 포함된 비트 필드로, 프로세서의 시스템 동작을 제어하거나 상태를 나타냅니다. 이 플래그들은 작업 전환, 인터럽트 처리, 트레이싱 등 시스템 운영에 필요한 기능을 제어합니다.

주요 시스템 플래그

- IF (Interrupt Enable Flag)

- 인터럽트 허용 여부를 제어합니다.

- 1: 인터럽트 활성화 (허용).

- 0: 인터럽트 비활성화 (무시).

- 운영체제가 인터럽트를 차단하거나 허용할 때 사용합니다.

- 인터럽트 허용 여부를 제어합니다.

- TF (Trap Flag)

- 단일 스텝 디버깅을 활성화합니다.

- 1: 명령어 실행 후 트랩 인터럽트가 발생하여 디버거로 제어가 전달됩니다.

- 단일 스텝 디버깅을 활성화합니다.

- NT (Nested Task Flag)

- 작업(Task) 간 중첩 호출을 나타냅니다.

- 1: 작업 전환이 중첩 상태임을 나타냄.

- 작업(Task) 간 중첩 호출을 나타냅니다.

- RF (Resume Flag)

- 디버깅 예외(예: Breakpoint Exception)를 재개할 때 사용.

- 1: 디버그 예외를 무시하고 명령어 실행을 재개합니다.

- 디버깅 예외(예: Breakpoint Exception)를 재개할 때 사용.

- VM (Virtual-8086 Mode Flag)

- 프로세서를 가상 8086 모드로 전환합니다.

- 1: 가상 8086 모드 활성화.

- 0: 보호 모드.

- 프로세서를 가상 8086 모드로 전환합니다.

2. IOPL 필드 (I/O Privilege Level Field)

IOPL의 정의

- *IOPL (I/O Privilege Level)**은 EFLAGS 레지스터의 12번과 13번 비트에 위치한 2비트 필드로, **입출력 명령어(IO instructions)**의 실행 권한을 제어합니다.

- 이 필드는 프로세스가 특정 **특권 레벨(Ring)**에서 실행될 때 IO 명령어 실행 가능 여부를 결정합니다.

IOPL 값과 권한

IOPL 값 허용된 레벨 (CPL) 설명

| 0 | Ring 0 (커널 모드)만 허용 | 가장 엄격한 권한 제어. |

| 1 | Ring 0~1 (커널 및 하위 레벨)만 허용 | 제한적 입출력 권한. |

| 2 | Ring 0~2 (커널 및 중간 수준 권한) 허용 | 일반 애플리케이션보다 높은 권한. |

| 3 | Ring 0~3 (모든 레벨) 허용 | 모든 애플리케이션에서 허용. |

IOPL 필드의 동작

- 현재 실행 중인 코드의 **권한 레벨(CPL)**과 IOPL을 비교하여 입출력 명령어의 실행 여부를 결정합니다.

- CPL ≤ IOPL: 입출력 명령어 실행 허용.

- CPL > IOPL: 입출력 명령어 실행 시 권한 예외(#GP) 발생.

IOPL의 활용

- 시스템 보안

- 입출력 명령어를 낮은 권한 레벨에서 실행하지 못하도록 제한하여 시스템 보안을 강화합니다.

- 운영체제 설계

- 운영체제는 IOPL 값을 설정하여 사용자 모드(Ring 3)에서의 IO 명령어 접근을 제한하고, 커널 모드(Ring 0)에서만 실행되도록 제어합니다.

- 특정 드라이버 실행

- IOPL을 조정하여 특정 드라이버나 하드웨어와의 상호작용을 제한적으로 허용할 수 있습니다.

IA-32 아키텍처의 운영 모드

1. Protected Mode (보호 모드)

- IA-32 프로세서의 기본 모드.

- 특징:

- 고급 기능 지원 (예: 메모리 보호, 멀티태스킹).

- 과거 소프트웨어와의 하위 호환성 제공.

- Paging과 Segmentation을 통한 가상 메모리 관리.

2. Real-Address Mode (실제 주소 모드)

- Intel 8086 프로세서의 환경을 제공합니다.

- 특징:

- 간단한 메모리 모델로, 기본적으로 1MB의 메모리 접근 가능.

- 일부 확장 기능 포함 (예: Protected Mode로 전환 가능).

- 프로세서는 초기화(Reset) 후 이 모드에서 시작됩니다.

3. System Management Mode (SMM)

- 프로세서의 특수한 운영 모드로, 전원 관리 및 하드웨어 제어를 위한 기능 제공.

- 특징:

- SMI# 핀 신호를 통해 진입.

- 현재 프로그램의 상태를 저장하고, 별도의 주소 공간에서 SMM 코드를 실행.

- RSM 명령어를 실행하면, 이전 모드로 복귀.

4. Virtual-8086 Mode (가상 8086 모드)

- Protected Mode의 하위 모드.

- 특징:

- Intel 8086 소프트웨어를 멀티태스킹 환경에서 실행 가능.

- EFLAGS 레지스터의 VM 플래그로 제어.

- Protected Mode에서 태스크 전환, 인터럽트 또는 예외 핸들러를 통해 진입.

Intel 64 아키텍처에서 추가된 운영 모드

1. IA-32e Mode (IA-32 확장 모드)

- IA-32e 모드는 64비트 모드와 **호환 모드(Compatibility Mode)**로 구성됩니다.

- 64비트 모드:

- 64비트 선형 주소를 지원.

- 64GB 이상의 물리 메모리 접근 가능.

- 호환 모드:

- 대부분의 기존 Protected Mode 애플리케이션을 변경 없이 실행 가능.

- 64비트 모드:

모드 간 전환

1. Real-Address Mode → Protected Mode

- CR0 레지스터의 PE(Protection Enable) 플래그를 설정하여 전환.

2. Protected Mode → Virtual-8086 Mode

- EFLAGS 레지스터의 VM(Virtual Mode) 플래그를 설정하여 진입.

- 태스크 전환 또는 인터럽트/예외 핸들러로 전환 수행.

3. Protected Mode → IA-32e Mode

- IA32_EFER 레지스터의 LME(Long Mode Enable) 플래그를 설정.

- Paging 활성화 필요.

4. SMM(System Management Mode)

- SMI# 핀 신호로 진입.

- RSM 명령어를 통해 이전 모드로 복귀.

기술적 플래그와 레지스터

- CR0 레지스터: PE 플래그를 통해 Real-Address Mode와 Protected Mode를 전환.

- EFLAGS 레지스터: VM 플래그로 Protected Mode와 Virtual-8086 Mode를 전환.

- IA32_EFER 레지스터:

- LME 플래그: IA-32e 모드 활성화.

- LMA 플래그: 64비트 모드와 호환 모드 결정.

- CS 레지스터의 L 비트: IA-32e 모드에서 현재 코드 세그먼트가 64비트 모드인지 호환 모드인지 결정.

시스템 플래그와 EFLAG

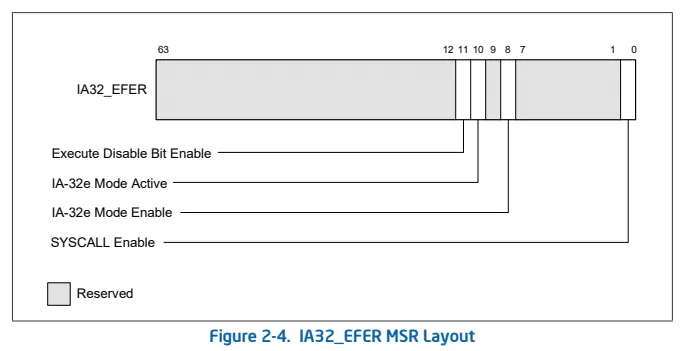

IA32_EFER 레지스터 필드 설명

- Bit 0 (SYSCALL Enable: IA32_EFER.SCE)

- 이 비트는 SYSCALL 및 SYSRET 명령어를 64비트 모드에서 활성화하거나 비활성화하는 데 씀

- R/W(읽기/쓰기 가능)로 설정할 수 있음.

- 예: 운영체제가 SYSCALL 명령어를 지원하려면 이 비트를 활성화해야 함.

- Bit 8 (IA-32e Mode Enable: IA32_EFER.LME)

- IA-32e 모드(64비트 모드)를 활성화하기 위한 비트.

- R/W로 설정 가능.

- IA-32e 모드로 전환하려면 이 비트를 1로 설정해야 하고, 페이징도 활성화해야 함.

- Bit 10 (IA-32e Mode Active: IA32_EFER.LMA)

- 현재 IA-32e 모드가 활성화되었는지를 나타내는 읽기 전용 비트.

- LME 비트가 설정되고 페이징이 활성화되면 자동으로 1로 설정됨.

- Bit 11 (Execute Disable Bit Enable: IA32_EFER.NXE)

- NX (No-eXecute) 비트를 활성화해서 특정 메모리 페이지에서 코드 실행을 막는 데 사용돼.

- 이를 통해 실행할 수 없는 메모리 영역에서의 명령 실행을 차단해 보안을 강화함.

- R/W로 설정 가능.

- 예: PAE(Page Address Extension)와 함께 사용하면 악성 코드의 실행을 방지할 수 있음.

- Reserved (비워진 비트)

- 나머지 비트들은 현재 사용되지 않고 예약된 상태

EFLAGS 주요 플래그와 필드

- TF (Trap Flag, Bit 8)

- 디버깅용 단일 단계 모드를 활성화하거나 비활성화.

- 1로 설정 시: 명령어 하나가 실행될 때마다 디버그 예외(#DB)가 발생.

- 디버깅 시 프로그램 상태를 한 명령어 단위로 점검할 수 있음.

- IF (Interrupt Enable Flag, Bit 9)

- 마스크 가능 하드웨어 인터럽트의 허용 여부를 제어.

- 1로 설정 시: 인터럽트를 허용.

- 예외(Exception)나 마스크 불가능 인터럽트(NMI)에는 영향을 주지 않음.

- IOPL (I/O Privilege Level, Bits 12-13)

- 현재 실행 중인 프로그램의 I/O 권한 레벨을 나타냄.

- 현재 프로그램의 **CPL(Current Privilege Level)**이 IOPL 이하일 때만 I/O 접근 가능.

- 권한 레벨이 낮아야 I/O 명령을 실행할 수 있어.

- NT (Nested Task Flag, Bit 14)

- 태스크 체인을 제어.

- 태스크 호출(CALL), 인터럽트, 예외가 발생하면 설정되고, IRET 명령으로 복귀할 때 사용.

- POPF/POPFD로 설정 가능하지만 예상치 못한 예외를 일으킬 수 있음.

- RF (Resume Flag, Bit 16)

- *디버그 예외(#DB)**를 임시로 비활성화.

- 디버깅 중 명령어가 재실행되면서 또 다른 예외가 발생하지 않도록 방지.

- 사용 후 자동으로 0으로 초기화됨.

- VM (Virtual-8086 Mode, Bit 17)

- Virtual-8086 모드 활성화 여부를 결정.

- 1로 설정 시: Virtual-8086 모드 활성화.

- 0으로 설정 시: Protected Mode로 복귀.

- AC (Alignment Check, Bit 18)

- 데이터의 메모리 정렬을 확인.

- CR0 레지스터의 AM 비트가 활성화된 경우에만 작동.

- 정렬되지 않은 데이터에 접근하면 예외 발생.

- VIF (Virtual Interrupt Flag, Bit 19)

- IF 플래그의 가상 이미지를 저장.

- VME 또는 PVI 플래그가 활성화된 경우에만 작동.

- VIP (Virtual Interrupt Pending, Bit 20)

- 소프트웨어에 의해 설정되며, 인터럽트가 대기 중임을 나타냄.

- 프로세서는 이 비트를 읽기만 하고 수정하지 않음.

- ID (Identification Flag, Bit 21)

- 이 플래그를 설정/해제할 수 있는지는 CPUID 명령 지원 여부를 나타냄.

RFLAG

- RFLAGS와 EFLAGS의 차이

- 64비트 모드에서는 기존의 EFLAGS 레지스터가 RFLAGS로 확장돼서 64비트 크기를 가짐.

- 하지만 상위 32비트는 사용되지 않고 예약된 상태(Reserved).

- Virtual-8086 모드 비활성화

- IA-32e 모드에서는 Virtual-8086 모드가 지원되지 않음.

- VM 비트(Virtual-8086 Mode Flag)를 설정하려 해도 무시됨.

- 이는 IA-32e 모드가 64비트 환경에 맞춰 동작하기 때문에 옛날 8086 소프트웨어를 지원할 필요가 없기 때문.

- IA-32e 모드에서는 Virtual-8086 모드가 지원되지 않음.

- NT(Nested Task) 비트 동작

- 프로세서는 IA-32e 모드에서 NT 비트를 자동으로 설정하지 않음.

- 하지만 소프트웨어는 NT 비트를 설정 가능.

- 단, NT 비트를 설정한 상태에서 IRET 명령을 실행하면 **일반 보호 예외(#GP)**가 발생.

- SYSCALL/SYSRET 명령어의 동작

- SYSCALL(시스템 호출)과 SYSRET(시스템 복귀) 명령은 RFLAGS/EFLAGS의 특정 비트를 제어 가능.

- 예를 들어, 명령 실행 중 특정 플래그를 저장하거나 복구할 수 있음.

- 이 동작은 프로그래밍 가능한 방식으로 설정돼서, 소프트웨어가 필요에 따라 플래그를 조정할 수 있음.

- SYSCALL(시스템 호출)과 SYSRET(시스템 복귀) 명령은 RFLAGS/EFLAGS의 특정 비트를 제어 가능.

IRET 명령이란?

- *IRET (Interrupt Return)**은 인터럽트 핸들러 실행이 끝난 후 CPU가 원래 실행하던 프로그램으로 복귀할 때 사용하는 명령.

이 명령은 인터럽트 처리 루틴의 마지막에 위치하며, 스택에 저장된 이전 실행 상태를 복구하는 역할을 함.

IRET 명령의 동작 과정

- IRET 실행 시 CPU가 복구하는 상태:

- EIP/RIP (Instruction Pointer): 중단되었던 명령어의 주소.

- CS (Code Segment): 코드 세그먼트 레지스터 값.

- EFLAGS/RFLAGS: 인터럽트 발생 전에 CPU의 상태 플래그.

- 프로세스:

- CPU는 스택에 저장된 값을 사용해 위 3가지 레지스터를 복구.

- 복구 후 원래 실행 중이던 코드로 복귀.

IA-32e 모드에서 IRET 명령이 GP (#GP)를 발생시키는 이유

- NT(Nested Task) 비트와 IRET의 관계:

- NT 비트는 Nested Task 플래그로, 태스크 간의 호출 체인을 관리하는 데 사용됨.

- 32비트 Protected Mode에서는 NT 비트가 설정된 경우, IRET 명령은 태스크를 전환하며 실행을 복구.

- 그러나 IA-32e 모드에서는 NT 비트를 사용하는 Nested Task 기능이 지원되지 않음.

- IRET 실행 시 NT 비트 확인:

- IA-32e 모드에서 IRET 명령은 스택에서 EFLAGS/RFLAGS 값을 복구하는 과정에서 NT 비트를 확인함.

- 만약 NT 비트가 1로 설정되어 있으면, 프로세서는 이를 잘못된 상태로 간주하고 **일반 보호 예외(GP, #GP)**를 발생시킴.

- 왜 GP(#GP)가 발생하는가?:

- IA-32e 모드에서는 NT 비트를 사용하는 기능이 금지되어 있음.

- IRET 명령이 NT 비트를 활성화된 상태로 복구하려고 하면, 이는 규격에 맞지 않은 동작으로 간주되므로 #GP 예외를 발생시킴.

메모리 관리 레지스터 개요

이 레지스터들은 CPU가 메모리를 효율적으로 관리하기 위해 사용하는 데이터 구조(GDT, LDT, IDT, TSS)의 위치와 크기를 저장한다.

- GDTR (Global Descriptor Table Register): 전역 디스크립터 테이블(GDT) 위치와 크기를 지정.

- LDTR (Local Descriptor Table Register): 로컬 디스크립터 테이블(LDT) 위치와 크기를 지정.

- IDTR (Interrupt Descriptor Table Register): 인터럽트 디스크립터 테이블(IDT) 위치와 크기를 지정.

- TR (Task Register): 현재 태스크의 태스크 상태 세그먼트(TSS) 정보를 지정.

2. 각 레지스터 설명

2.1 GDTR (Global Descriptor Table Register)

- 역할: 전역 디스크립터 테이블(GDT)의 **기본 주소(Base Address)**와 **테이블 크기(Limit)**를 저장.

- GDT는 세그먼트의 속성(베이스 주소, 크기, 접근 권한 등)을 정의하는 테이블.

- 구조:

- 32비트 모드: 32비트 기본 주소와 16비트 크기.

- 64비트 모드: 64비트 기본 주소와 16비트 크기.

- 초기화:

- CPU가 리셋되면 기본 주소는 0으로, 크기는 0xFFFF로 설정됨.

- 보호 모드 사용 시 반드시 새 값으로 초기화 필요.

- 명령어:

- LGDT: GDTR 값을 로드.

- SGDT: GDTR 값을 저장.

2.2 LDTR (Local Descriptor Table Register)

- 역할: 로컬 디스크립터 테이블(LDT)의 기본 주소(Base Address), 크기(Limit), 그리고 디스크립터 속성을 저장.

- LDT는 특정 태스크나 프로그램에 필요한 세그먼트 디스크립터를 관리.

- 구조:

- 32비트 모드: 32비트 기본 주소와 16비트 크기.

- 64비트 모드: 64비트 기본 주소와 16비트 크기.

- 초기화:

- CPU가 리셋되면 기본 주소는 0, 크기는 0xFFFF로 설정.

- LLDT 명령으로 LDTR 초기화 가능.

- 명령어:

- LLDT: LDTR 값을 로드.

- SLDT: LDTR 값을 저장.

2.3 IDTR (Interrupt Descriptor Table Register)

- 역할: 인터럽트 디스크립터 테이블(IDT)의 기본 주소(Base Address)와 크기(Limit)를 저장.

- IDT는 인터럽트 및 예외 처리 루틴의 위치와 속성을 정의.

- 구조:

- 32비트 모드: 32비트 기본 주소와 16비트 크기.

- 64비트 모드: 64비트 기본 주소와 16비트 크기.

- 초기화:

- CPU가 리셋되면 기본 주소는 0, 크기는 0xFFFF로 설정.

- 인터럽트 처리 루틴을 등록하려면 초기화 필요.

- 명령어:

- LIDT: IDTR 값을 로드.

- SIDT: IDTR 값을 저장.

2.4 TR (Task Register)

- 역할: 현재 태스크의 태스크 상태 세그먼트(TSS) 정보를 저장.

- TSS는 태스크 간의 전환 시 레지스터 값, 스택 포인터 등을 저장하는 데 사용.

- 구조:

- 32비트 모드: 32비트 기본 주소와 16비트 크기.

- 64비트 모드: 64비트 기본 주소와 16비트 크기.

- 초기화:

- CPU가 리셋되면 기본 주소는 0, 크기는 0xFFFF로 설정.

- 새로운 태스크로 전환될 때 자동으로 업데이트.

- 명령어:

- LTR: TR 값을 로드.

- STR: TR 값을 저장.

3. 세그먼트 관리의 주요 흐름

- GDTR: 시스템 전반의 세그먼트 정보(GDT)를 관리.

- LDTR: 특정 태스크나 프로그램의 세그먼트 정보(LDT)를 관리.

- IDTR: 인터럽트와 예외 처리를 위한 IDT를 관리.

- TR: 현재 실행 중인 태스크의 상태(TSS)를 관리.

4. 초기화와 동작

- CPU가 전원을 켜거나 리셋되면 모든 레지스터 값은 기본값(0 또는 0xFFFF)으로 설정됨.

- 보호 모드(Protected Mode) 또는 IA-32e 모드로 전환하려면 GDTR과 IDTR 등의 레지스터를 반드시 초기화해야 함.

- 태스크 전환 시, LDTR과 TR은 새로운 태스크의 디스크립터 정보를 자동으로 로드.

2.5 CONTROL REGISTERS 요약

- CR0, CR1, CR2, CR3, CR4, CR8로 구성.

- 32비트 모드에서는 32비트, 64비트 모드에서는 64비트 크기로 확장.

- 제어 레지스터는 MOV 명령어를 통해 읽기/쓰기 가능하며, 권한 레벨 0에서만 접근 가능.

- *예약된 비트(Reserved Bits)**는 반드시 0으로 설정해야 하며, 잘못된 설정은 예외(#GP)를 발생시킴.

각 레지스터의 역할

1. CR0 (Control Register 0)

- CPU의 시스템 제어 플래그를 포함.

- 운영 모드와 CPU 상태를 제어.

- 보호 모드(Protected Mode)와 가상 메모리(Paging) 활성화 플래그가 포함됨.

- 예: PE(Protection Enable), PG(Paging Enable), CD(Cache Disable).

2. CR1

- 예약됨(Reserved): 사용되지 않음.

3. CR2

- *페이지 폴트 주소(Page-Fault Linear Address)**를 저장.

- 페이지 폴트가 발생한 메모리 주소를 제공해 디버깅과 예외 처리를 지원.

- 모든 64비트가 쓰기 가능.

4. CR3

- 페이징 구조의 루트 주소를 저장.

- 페이지 디렉터리, PML4 테이블, PML5 테이블의 물리 주소(Base Address) 포함.

- *PCD (Page Cache Disable)**와 PWT (Page Write Through) 플래그를 포함.

- 페이징 구조의 캐싱을 제어.

- 12비트 정렬 필요:

- 하위 12비트는 항상 0이어야 하며, 페이지 경계(4KB)로 정렬되어야 함.

- Physical Address Extension(PAE), 4-Level Paging, 5-Level Paging 지원.

- 4 레벨 페이징 및 5 레벨 페이징을 사용하는 경우 CR3 레지스터에는 PML4의 기본 주소가 포함됩니다.

5. CR4

- 아키텍처 확장 기능을 활성화하는 플래그 그룹 포함.

- 예: PAE(Physical Address Extension), SSE(Streaming SIMD Extensions), SMAP(Supervisor Mode Access Prevention).

- 64비트 모드 전용 비트 (CR4[63:32]):

- IA-32e 모드(64비트 모드)에서만 사용 가능.

- 64비트 모드 밖에서는 효과 없음.

6. CR8 (64비트 모드 전용)

- *Task Priority Register (TPR)**에 대한 읽기/쓰기 접근 제공.

- 외부 인터럽트의 우선순위를 제어.

- 64비트 모드에서만 사용 가능.

- 호환 모드(Compatibility Mode)에서도 인터럽트 필터링은 계속 적용됨.

사용 및 제약 사항

- 권한 레벨 0에서만 접근 가능:

- 운영체제와 같은 특권 코드만 제어 레지스터를 읽거나 쓸 수 있음.

- 권한 레벨 1, 2, 3에서는 접근 불가.

- 예약된 비트 사용 제한:

- CR0[31:0]의 예약된 비트를 설정하려 하면 무시됨.

- CR0[63:32] 또는 CR4의 예약된 비트를 설정하면 #GP(0) 예외가 발생.

- MOV 명령 동작:

- 64비트 모드에서 MOV 명령은 상위 32비트를 포함한 모든 비트를 유지.

- 64비트 모드 외부에서 MOV 명령 실행 시 상위 32비트는 0으로 초기화됨.

CR0 플래그 정리

- CR0.PG (Paging, 비트 31)

- 페이징 활성화/비활성화를 제어.

- 1로 설정: 페이징 활성화 → 가상 주소를 물리 주소로 매핑.

- 0으로 설정: 페이징 비활성화 → 모든 주소를 물리 주소로 처리.

- 주의: PE(Protection Enable) 플래그가 설정되지 않은 상태에서 PG를 설정하면 #GP(일반 보호 예외) 발생.

- CR0.CD (Cache Disable, 비트 30)

- 캐시 비활성화를 제어.

- 1로 설정: 프로세서의 캐시 접근 제한.

- 캐시를 비활성화하려면 CD를 설정하고 캐시를 무효화해야 함.

- CR0.NW (Not Write-through, 비트 29)

- 쓰기 처리 방식(Write-through 또는 Write-back)을 결정.

- 0으로 설정: 캐시에 Write-back 활성화 (데이터를 캐시에 먼저 쓰고 나중에 메모리에 씀).

- 1로 설정: Write-through 활성화 (데이터를 캐시와 메모리에 동시에 씀).

- CR0.AM (Alignment Mask, 비트 18)

- 메모리 정렬 검사를 제어.

- 1로 설정: 정렬되지 않은 메모리 접근 시 예외 발생.

- 조건: AM 플래그, EFLAGS.AC 플래그가 1이고, CPL이 3(사용자 모드)일 때.

- CR0.WP (Write Protect, 비트 16)

- 슈퍼바이저 레벨에서 읽기 전용 페이지 쓰기를 제어.

- 1로 설정: 읽기 전용 페이지에 쓰기 금지.

- 0으로 설정: 읽기 전용 페이지에 쓰기 가능.

- OS에서 Copy-on-Write(COW) 구현에 사용.

- CR0.NE (Numeric Error, 비트 5)

- x87 FPU 에러 보고 메커니즘을 제어.

- 1로 설정: 내부(native) 방식으로 에러 보고.

- 0으로 설정: PC 스타일의 외부 핀(FERR#, IGNNE#)을 사용한 에러 보고.

- 현대 OS에서는 이 비트를 1로 설정해 내부 방식 사용을 권장.

- CR0.ET (Extension Type, 비트 4)

- 구식 플래그로, Intel 386/486 프로세서에서 사용.

- 최신 프로세서에서는 항상 1로 고정되어 있음.

- CR0.TS (Task Switched, 비트 3)

- 태스크 전환 시 FPU/MMX/SSE 레지스터 상태 저장 지연을 제어.

- 1로 설정: 태스크 전환 후 FPU/MMX/SSE 명령어를 실행하면 #NM 예외 발생.

- 예외 핸들러가 FPU/MMX/SSE 상태를 저장하고 TS 플래그를 초기화(Clear)해야 함.

- 새로운 태스크에서 FPU 명령어를 실행하지 않으면 레지스터 상태를 저장하지 않아도 됨.

- CR0.EM (Emulation, 비트 2)

- FPU 명령어 에뮬레이션을 제어.

- 1로 설정: FPU 명령어를 소프트웨어 에뮬레이션으로 실행.

- 0으로 설정: 하드웨어 FPU에서 실행.

- CR0.MP (Monitor Coprocessor, 비트 1)

- x87 FPU와 WAIT/FWAIT 명령어의 사용 조건을 제어.

- MP 플래그와 TS 플래그를 함께 사용해 FPU 사용 여부를 결정.

2. CR3 레지스터 (Control Register 3)

CR3는 페이징 구조의 루트 주소와 캐시 동작을 제어.

플래그 이름 비트 설명

| PCD | Page-level Cache Disable | 4 | 페이징 구조의 캐싱을 비활성화. |

| PWT | Page-level Write-Through | 3 | 페이징 구조의 쓰기 처리 방식을 제어 (Write-through 또는 Write-back). |

| LAM_U57 | User LAM57 Enable | 61 | 사용자 포인터에서 선형 주소 비트 62:57 마스킹 활성화. |

| LAM_U48 | User LAM48 Enable | 62 | 사용자 포인터에서 선형 주소 비트 62:48 마스킹 활성화. |

3. CR4 레지스터 (Control Register 4)

CR4는 프로세서의 확장 기능을 활성화하거나 제어하는 플래그를 포함함.

플래그 이름 비트 설명

| VME | Virtual-8086 Mode Extensions | 0 | Virtual-8086 모드에서 인터럽트 및 예외 처리 확장을 활성화. |

| PVI | Protected-Mode Virtual Interrupts | 1 | 보호 모드에서 가상 인터럽트 플래그(VIF) 활성화. |

| TSD | Time Stamp Disable | 2 | RDTSC 명령어를 권한 레벨 0에서만 실행 가능하도록 제한. |

| DE | Debugging Extensions | 3 | DR4, DR5 레지스터 접근 시 #UD 예외 발생. |

| PSE | Page Size Extensions | 4 | 32비트 페이징에서 4MB 페이지 활성화. |

| PAE | Physical Address Extension | 5 | 물리 주소 확장 활성화. 32비트를 초과하는 물리 주소를 지원. |

| MCE | Machine-Check Enable | 6 | Machine Check Exception 활성화. |

| PGE | Page Global Enable | 7 | 글로벌 페이지를 활성화해 TLB 플러시 시 제외. |

| PCE | Performance-Monitoring Counter Enable | 8 | RDPMC 명령어를 모든 보호 레벨에서 실행 가능. |

| OSFXSR | OS Support for FXSAVE/FXRSTOR Instructions | 9 | FXSAVE/FXRSTOR 명령어와 SSE/SSE2/SSE3/SSSE3/SSE4 지원 활성화. |

| OSXMMEXCPT | OS Support for SIMD Floating-Point Exceptions | 10 | SIMD 부동소수점 예외(#XM)를 처리하는 운영체제 지원 활성화. |

| UMIP | User-Mode Instruction Prevention | 11 | 사용자 모드에서 특정 명령어(SGDT, SIDT 등) 실행 금지. |

| LA57 | 57-bit Linear Addressing | 12 | 57비트 선형 주소 지원(5레벨 페이징). |

| VMXE | VMX Enable | 13 | VMX(Virtual Machine Extensions) 활성화. |

| SMXE | SMX Enable | 14 | SMX(Safer Mode Extensions) 활성화. |

| FSGSBASE | FS/GS Base Enable | 16 | RDFSBASE, WRFSBASE 등의 명령어 활성화. |

| PCIDE | PCID Enable | 17 | 프로세스 컨텍스트 식별자(PCID) 활성화. IA-32e 모드에서만 사용 가능. |

| OSXSAVE | XSAVE and Processor Extended States Enable | 18 | XSAVE/XRSTOR 명령어 및 확장 상태 지원 활성화. |

| KL | Key Locker Enable | 19 | AES Key Locker 명령어 활성화. |

| SMEP | Supervisor Mode Execution Prevention | 20 | 커널에서 사용자 모드 코드를 실행하지 못하도록 방지. |

| SMAP | Supervisor Mode Access Prevention | 21 | 커널에서 사용자 모드 메모리 접근을 방지. |

| PKE | Protection Keys for User-Mode Pages | 22 | 사용자 모드 메모리 페이지의 보호 키 활성화. |

| CET | Control-Flow Enforcement Technology | 23 | 제어 흐름 보호 기술 활성화. |

| PKS | Protection Keys for Supervisor-Mode Pages | 24 | 커널 모드 메모리 페이지의 보호 키 활성화. |

| UINTR | User Interrupts Enable | 25 | 사용자 인터럽트 지원 활성화. |

| LAM_SUP | Supervisor Linear-Address Masking | 28 | 커널 주소의 선형 주소 마스킹 활성화. |

4. CR8 레지스터 (Control Register 8, 64비트 모드 전용)

CR8는 외부 인터럽트의 우선순위를 제어.

플래그 이름 비트 설명

| TPL | Task Priority Level | 3:0 | 인터럽트 우선순위 임계값 설정. 0은 모든 인터럽트 허용, 15는 모든 인터럽트 차단. |

'Research' 카테고리의 다른 글

| SeedSeeker (1) | 2024.02.18 |

|---|---|

| ComRaceConditionSeeker (0) | 2024.02.13 |

| CodeQL Summary (1) | 2024.02.06 |

| What Is Windows Search DB? (1) | 2023.12.26 |

| Twice the Bits, Twice the Trouble: Vulnerabilities Induced by Migrating to 64-Bit Platforms (2) | 2023.11.22 |

소중한 공감 감사합니다